# 新たな ICAP/4 リリースに追加される DSP Designer

### DSP Designer とは?

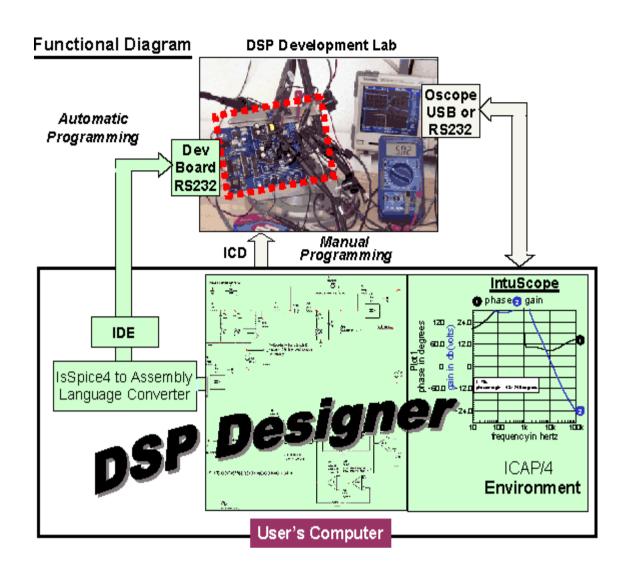

スイートを使用した DSP デザインの革新的な製品です。特別なデバイスのモデルが DSP デジタル制御をプログラミングするために、伝達関数と等価のアセンブリコード命令をシミュレートするためのビジュアル的な方法を提供します。 Z 変換に隠れたパラメータの Bode プロットを含むデザインのコレスポンディング波形を表示することができます。 本製品は、 DSP アイドル処理として実行している開発ボードインタフェースから入力された DSP アセンブリ言語プログラミングを検証するために利用できます。 DSP Designer の詳細情報については www.intusoft.com を参照してください。

### DSP Designer はどのように動作するのか?

#### 問題

リアルタイムの信号処理のコーディングは長く、エラーを起こしやすいです。表面上「正しい」ときでも、エラーは通常存在します。よりよいアルゴリズムが実装することができるように DSP で要求される詳細なマイクロ・コード・ブックから、エンジニアを開放するためコンピュータの自動化が必要となります。 SPICE を使用したシミュレーションは部分的に問題を解決します。 Z 変換、Z-1 のため SPICE のディレイ回路を代用することは通常のアプローチです。しかし、複雑さが増すことによって代用が意味なくなるので、不安定性が原因でサンプリング周波数以上は、明らかに不可能です。さらに厄介なのは、代数「フィードバック」が発生した際に増す複雑さです。

シンプルなバックレギュレータ・プラント・モデルを例に上げます。出力電圧は、出力及び入力電圧の差に対して比例するインダクタの電流で入力にフィードバックします。

しかし出力電圧は、この差に比例します。よりよいソリューションは代数方程式を解くことですが、最もシンプルな見積りは、この不快なフィードバックを遮断するために、後方オイラー積分を使用することです。しかも、詳細なインプリメンテーションはエラーが起こりやすいので設計者は性能の低下を受け、それに伴うジョブが生じます。さらに大部分の DSP 変数はコードに隠れているので、シミュレーション予測を確認することができません。

### <u>ソリューション</u>

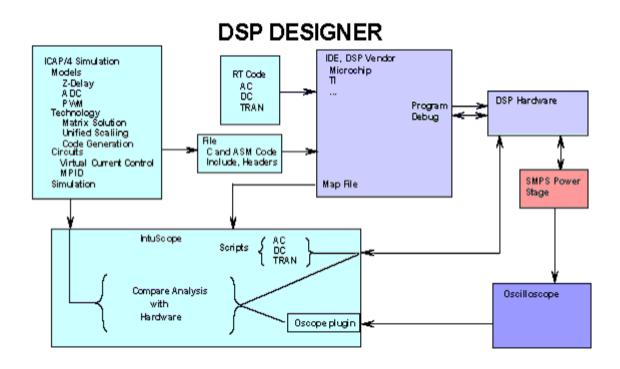

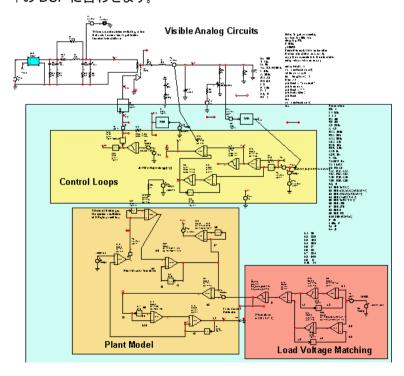

DSP Designer は、Intusoft の ICAP/4 SPICE ツールセットをベースにしたソフトウェア/ファームウェア・スイートです。 Z 変換 ベースのモデリングを高速且つ簡単に作るためのシミュレーションモデルが追加されました。これはさらに完全な遅延モデルを得るために z-delay で開始、次に良好なアナログ・デジタル・コンバータ・モデル内に追加します。これは周波数とタイムドメインの両方のエラーを量子化することで対応します。連続導通モードの PWM モデルは最も高速なシミュレーションのために使用します。SpiceNet のコンフィギラブル・スケマティックで構築、複数の制御ループが分割され、安定化パラメータ、利得、位相余裕を測定するために数秒でシミュレーションします。IsSpice4のマトリックス・ソリューションは、DSP制御システムを記述している微分方程式のセットを抽出するために使用されます。これらの方程式は、最適な積和演算(MAC)命令の実行のために再アレンジされます。様々なベンダの DSP のための特別なプラグインは、ソフトウェアプロジェクトに対して実行することができる C 及びアセンブリ・レベルのコードを生成します。統一されたスケーリングアプローチは、シミュレーションをスケールする方法を示し、整数、ミックスド、あるいはフラクショナルスケーリングのために正しい DSP 係数を計算することを実証します。

例題回路は、修正、比例、積分、微分、MPID デザインを含むターゲットデザイン用に提供されます。また Virtual Current Controller の電流フィードバックのための新しいコンセプトも開発されました。これらのコントローラの両方が、Mirochip 及び Texas Instruments のテスト環境を使用したハードウェアでインプリメントされています。

シミュレーションは、通常 AC、DC、TRA のために実行できます。DSP で同じ機能を提供するために、リアルタイム(RT)コードが提供されます。これは本機能を提供するために DSP ヘシリアルインタフェースでリンクします。最も、挑戦的な部分は、DSP の内部の伝達関数アナライザ(TFA)の導入です。TFA は、ICAP/4ソフトウェア内部の単一のインジェクション・モデリング。テクニックを使用します。IntuScope スクリプトは DSP シリアルインタフェースを制御するために用いられ、RT コードを使用して、自動化されたスクリプトが測定結果を生成、表示します。

すべての DSP が、SMPS パワー段を持っているというわけではありません。Intusoft は、それが利用できないケースのためにブレッドボードに組まれる必要がある必須の回路スケマティックを提供します。

実験のオシロスコープ測定波形を表示するために IntuScope 内へシリアルリンクで転送することができるよう、新たなデータ収集プラグインが IntuScope に追加されました。

### DSP Designer を使用してシミュレーションするのはなぜか?

DSP 開発ボードで使用しているアセンブリ命令の従来のプログラミングはたいへん長〈エラーも起こりやすいというのは周知の事実です。コーディングのミスはよ〈あり、頻繁に検出することな〈デジタル制御処理を通過します。また、伝達関数内で隠れている変数を解析することは不可能です。しかし DSP Designer によって提供された特別なデバイスモデルを使用したマイクロインストラクションのシミュレーションによってデザインのビジュアル的なアプローチがしやす〈なり、デジタル制御処理の波形を表示でき、簡単にこれとデザインの他の面をデバッグできます。一旦満たされたら、スケマティックは開発ボードのメモリに自動的に記述されるよう正しいアセンブリコード命令をするのに使用することができます。この処理が自動化されたバージョンは現在開発中で 2009 年 Q1 にリリース予定です。

もし、最初のうちはマニュアルでの DSP のコーディングを希望する場合、デバイスモデル及び波形を経たコードをシミュレートすることでアセンブリ言語を認証するため DSP Designer を後で使用することができます。また、ツールセットはパワー分野、フィルタリング、A/D、D/A 変換のような DSP の他の面をシミュレートすることもできます。

# DSP Designer の利点

#### 信頼性の向上

コーディングエラーは DSP のデジタル制御アルゴリズムをビジュアル的にシミュレートし、コレスポンディング波形を表示することによって、削除されます。 伝達関数解析の DSP コーディングに通常存在する"Hidden" 変数は、親しみのある IsSpice4、AC、OP、TRAN解析、DSPのテストコードを使用、DSPとIntuScope 間の自動通信で波形を表示することによって、DSP Designer 内で見つけることができます。

#### 時間短縮

IsSpice4 シミュレーションを使用したビジュアル・デザインアプローチは、時間とアセンブリ命令の長く、エラーの起こりやすいプログラミングを短縮します。 IsSpice4 での DSP/CPU の DSP Designer の自動化されたプログラミングはさらに時間を 短縮します。

#### 部品の低減

デジタル制御処理にそれらの関数を構築することによって部品を低減することができます。例えば、直接電流をセンスすることなく、スイッチのインダクタ電流を得るため DSP plant model を使用する等

#### 市場出荷の改善

上記の利点は、素早い市場投入とより高い製品信頼性につながります。

#### ターンキー・シミュレーション・ツール・スイート

DSP Designer は磁気デザイン及びテストシンセシス・ソフトウェアを含む最も高度で利用が簡単なアナログ、ミックスドシグナル、ミックスドシステム・シミュレーションセットの一部です。Intusoft のスケーラブルな ICAP/4 ソフトウェア提供や Test Designer は様々な種類のデザインシミュレーション、検証、テスト、ドキュメンテーションのために有益になります。

## DSP Designer はいつリリースされるのか?

DSP Designer の最初の機能は、2009 年 1 月の ICAP/4 及び Test Designer リリースに含まれます。これは IntuScope 内に実験波形のファームウェア取り込みのためにオシロスコープ・プラグインを含みます。それは IDE を通じたアセンブリ命令をプログラムする為の DSP 開発ボードのメモリへの自動の IsSpcie4 通信をまだ含んでいません。DSP Designer は追加費用なしで Intusoft の ICAP/4 Windows Power Deluxe、ICAP/4 Windows、Power/RF Deluxe、Power Supply Designer、ICAP/4 Professional、Test Designer 製品に含まれる予定です。新たな MagneticsDesigner も 1 月にリリースされる予定です。

## DSP Designer はどの DSP 開発ボートや実験装置をインタフェースするのか?

Intusoft はある会社のカスタム DSP 開発ボードを調査しています。これは最大平均電力 200W で 12-30VDC 高電圧入力、0-30VDC 出力で Dual Buck/Boost synchronus SMPS で構成されています。実証されたら、2009 年の 1 月にリリースする予定です。

MicroChip dsPICDEM SMPS Buck 開発ボードは、本来 Intusoft 社の DSP Designer 動作のために使用されていましたが、たくさんの修正を要求しました。MicroChip の新たなボードが現在使用されていますが、まだ正式にはリリースされていません。これは 2009 年 1 月にリリースする予定です。

Texas Instruments/Spectrum Digital Board 2812eZdsp kit も DSP Designer で使用されます。しかしながら、ピギーバックボードがあり、Intusoft は DSP 開発のためにそれに取り付けました。Intusoft はそのカスタム DSP 開発ボードを調査しています。これは、最大平均電力 200W で、12-30VDC 高電圧入力、0-30VDC 出力、Dual Buck/Boost synchronus SMPSで構成されています。実証されたら、2009 年の 1 月にリリースする予定です。

USB インタフェースでの Tektronix TDS1012B オシロスコープ と RS232 シリアルインタフェースでの Tektronix TPS2014 の波形取り込みをサポートしています。他のシリーズの 1000 と 2000 スコープは通信インターフェースを使用して動作します。

# DSP 開発ボードへの DSP Designer の通信/プログラミング

DSP Designer をオシロスコープに接続するシリアルインタフェースは MicroChip SMPS Buck 評価ボードに含まれた RS232C 接続を使用します。Texas Instruments は類似したインタフェースを持っていますが、異なるプロトコルを使用します。その目的は、メモリへの読み書き(peak/poke)が可能な低いオーバーヘッド・バックグランド処理にすることです。 Intusoft のコード・ジェネレータはシンボル名(ノード名)を DSP メモリ・ロケーションと連携させます。 DSP を起動し安定状態で実行していると、これらのロケーションのメモリ値の読み込みと IsSpice4、IsSpice4 の OP (operating point 値)で使用されたフローティングポイント表示にそれらを戻すことができます。コードが DSP Designer を使用して生成した場合、スケールファクタが分かります。もしくは、ユーザは DSP が"one"を表す整数値を入力する必要があります。 IsSpice4 フローティングポイント値を得るために signed integer values は"one"で割られます。これらの値は、フローティングポイント値から IsSpice4 ノード値に変換するために A/D スケールファクタによる更なる変換が必要です。これらの数値を初期化するために DSP ボタンが IntuScope の"Add Waveforms"ダイアログに追加されています。この情報はそれぞれのプロジェクト (SpiceNet のドローイング名)毎にレジストリに格納されます。DSP は IntuScope "Browse" ボタンを使ってこれらの値にアクセスします。IntuScope はベクタ長 1 変数を"plot"データストラクチャに書き込んで Output ウィンドウ内でリストとして表示するという新たな機能を装備しています。またスクリプトはアクティブなシュミレーションの OP プロット値と DSP OP 値を比較するために作成されています。

トランジェント解析については DSP はステップ・ロード・テスト用に設定しています。これは既存のコードと DSP SMPS 評価ボードに搭載されたハードウェアの一部で、ユーザがデザインしたボードには追加のテストハードウェアが必要になります。このハードウェアは外部のテストセットアップの一部にすることが可能ですが、負荷スイッチングを動作させるには繰り返し信号を DSP デジタルポートから転送する必要があります。トランジェントのベクタは負荷スイッチ周期毎に 1 ポイント追加することによって作られます。最初のポイントは負荷スイッチの直前に得られます。後続のポイントは PWM サンプルによって遅れます。これは Tsample と呼ばれ、全体の波形が(Switch period) /Tsample に収集されます。100Hz (Tswperiod=10ms)の負荷スイッチング実行と 100KHz (Tsample=10us)での計算サイクルに関しては、波形が 1000 ポイントで 10 秒かかります。DSP のバックグランド負荷は全体の性能に比べて小さいです。19,200 Baud での RS232 の実行は、10 テストポイントまでモニタすることができます。

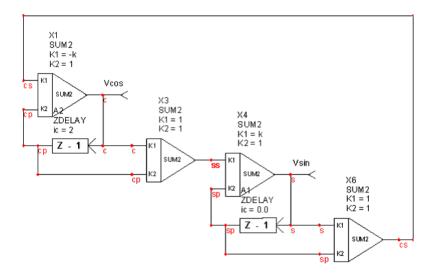

AC 解析については、サイン/コサイン・ジェネレータが DSP ファームウェアにプログラム化されています。 これは、30mip 命令レートで約 15 命令あるいは約 0.5usec 必要で、以下のことがあります:

周波数を評価するために設定される4つの係数

サイン、コサイン、以前のサイン、以前のコサインの4つのデータワード

処理を制御するための TFAtime という 1 つのデータワード

信号レベルを計るための Vsig という 1 つのデータワード

メモリワード TFAtime は、DSP のタイマ・レジスタとして使用され、0 に初期化されています。TFAtime ワードがシリアル・インタフェースを使用して 0x1 に設定されるまで DSP は TFA(Transfer Function Analysis)コード・セクションを入力しません。 DSP がアイドルループのこの条件を認識した時に初期化しサイン・コサイン・ジェネレータを開始します。ジェネレータは、この状態で永久に実行します。 TFAtime >= 0x2 の時、データ累積フェーズが開始します。 次に、各 Tsample インタラプトの終わりには Vout\*sine と Vout\*cosine の合計が累積され TFAtime が増加します。この計算は PWM デューティ比を設定後、

実行されるので計算遅延は追加せず、A/D インタラブトの終わりに"spare"タイムを使用します。TFAtime =TFAperiod の時、データ累積は停止します。アイドルループが TFAtime==TFAperiod を認識した時 TFAtime=0 に設定され、累積されたデータ(Vout)が RS232インターフェースを使用して Intuscope に転送されます。次に Scope はデータを拡大し、以前に初期化された TFA 周波数のために Vin=Vout+Vsig を計算します。Scope は次の周波数に進み、この処理を繰り返します。新しい IntuScope スクリプトではこれが全て実行されるので完了した際 Bode Plot が自動的に生成されます。ユーザは Vsig=Ksig\*sine を Vout でのデータに追加し、それを Vin に置く Vout テストポイントを挿入する必要があります。これは SpiceNet で単一の電圧インジェクション GFT を設定すると同じようなことです。しかし、Vin は IntuScope を使用して Vout + Vsig として計算することが可能であるので、Vinを測定する必要はありません。DSP Designer をコードジェネレータとして使用することがデフォルトの場合、Vout は PWM デューティ比が制限する前に計算され、Vin は PWM リミッタとして表すことができます。

TFA をプログラミングする際に理解しておく必要がある細かいポイントがいくつかあります。まず(TFAperiod-2)\* Tsample は整数のテスト周波数の周期が含まれる必要があります。これはテスト信号が同時に開始、完了することになります。その条件は TFA スクリプトで計算され、実際のテスト周波数が所望の値から若干変わってしまう原因となります。この条件を満足させる為に厳密な TFA 周波数を制限することは、DFT (Discrete Fourier Transform)解析のウィンドーイングを使う時によく行われるフーリエ係数からの誤差を排除します。

2 つ目は周波数を変更後、トランジェントの残りを安定化させることが必要です。 デフォルトはセトリングのために 50ms、データ累積のために 50m を使用します。

3つ目に、Vsig は Duty Ratio 制限を回避するのに十分小さくする必要があります。Vsig が全周波数スイープのため一定にした場合、低い周波数で正確なデータを得るには小さすぎる可能性があります。良好な制御システムデザインはオクタープ毎に良好な制御システムで毎オクターブ6dB減らすループゲインを持っています。従って、Vin の信号強度は"best"デッドビート・コントローラ用に概算されます。このケースでの以下の計算は約0.1 p-p でのデューティ比信号定数の作成方法を示しています。

まずサインは 2.14、コントローラは 8.8 でスケールされていますので、このサインは 2^8/2^14=2^-6 でスケールされる必要があります。

次に(Vout+Vsig)\*A=Vout

$Vout^*A-Vout = -Vsig^*A$

Vout=-Vsig/((A-1)

Vd=Vout+Vsig=Vsig/(1-A)+Vsig=Vsig\*(1+1/(1-A))

Vd=(2-A)/(1-A)

# DSP デザインの"ZDelay"コードモデル

制御システムのデザインと解析は通常周波数ドメインで実行されます。これによって、畳み込みのタイムドメイン処理は、周波数ドメインの単純な掛け算でリプレイスされます。 DSP デザインではサンプルされたデータシステムは基本的なビルディング・ブロックとして、ユニット・ディレイを利用した類似のコンセプトを使用します。 ディスクリート z-plane にマッピングされた s-plane は以下で導かれます。

$$Z^{-1} = e^{-sT}$$

$Z^{"}$  はnT秒のユニット・ディレイを表します。Sドメイン伝達関数は $Z^{"}$  多項式の比に変換されます。

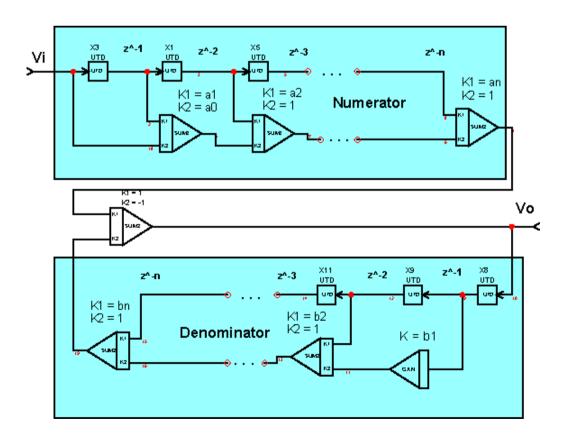

$$\frac{V_o}{V_i} = \frac{a_0 + a_1 z^{-1} + a_2 z^{-2} + \dots \cdot a_n z^{-n}}{1 + b_1 z^{-1} + b_2 z^{-2} + \dots \cdot b_n z^{-n}}$$

方程式は Vout を解くために更に整理することができ、IsSpice4 伝送線を使用してインプリメントされたユニット・タイム・ディレイ(UTD)を用いた以下のブロックダイアグラムに示された通り、ダイレクトなプログラミング方法を使用してインプリメントされます。このインプメントはトランジェントと AC 解析(Bode プロット等)の両方を含んだタイムドメインの差分方程式のIsSpice4 解析を実行できます。

新たなモデルZdelay が開発されました。これは従来の UTD 伝送線 IsSpice4 モデルより優れた収束とメモリ利用を持っています。この新しいモデルは Intusoft の Code Model SDK ツールを使用してインプリメントされました。本モデルは複数のユーザ指定パラメータで大幅にカスタマイズすることができます。これらのパラメータはスタートアップ・ディレイ、サンプリング・タイム、プロパゲーション・タイム、初期状態、高低出力制限を含んでいます。 DSP と通常のサンプル&ホールドアプリケーションに関して、Zdelay は伝送線型のモデルよりもカスタマイズ可能で、優れたパフォーマンスであることから好ましいモデルです。

例題として、図1に示されたサイン・コサイン波形ジェネレータを考えます。ここでは新しい Zdelay モデルを使用しています。 初期状態は回路をキックスタートする必要があることに注意して⟨ださい。必要な初期状態(IC)値をディレイモデルで指定す ることによって簡単に実現できます。

図 1, サイン・コサイン波形ジェネレータ

2KHz で生成されたサイン・コサイン波形が図2に示されています。

図 2, 2KHz のサイン及びコサイン波形生成

### IsSpice4 を使用したデジタルコントローラのデザイン

下図3に示したように共通の入出力グランドでの連続導通モード(CCM)で動作するバックレギュレータを考えてみます。スケマティックがUTDモデルと共に示されていることに注意してください。これは最終的に、より簡単に記述された Zdelay モデルに置き換えられます。IsSpice4 は variable タイムステップを使用することによって連続時間の関数をモデル化できます。本機能は連続時間のアナログモデルを生成するために使用します。次に連続時間モデルはゼロオーダー・ホールドによる Zドメインベースのモデルに変換されます。そして z ドメイン方程式はよく知られる Infinite Impulse Response(IIR)DSP 方程式に再整理されます。

IsSpice4 はこれらの連立方程式を解くためにマトリックスを構築します。これらの方程式はリニアであり、各ステップ毎のマトリックスを作りかえる必要はありません。これらの方程式を解くために IsSpice4 を使用するだけでなくフィードバック・パスを遮断するために通常挿入されるディレイも削除します。またマトリックス・オーダは、有限語長システムで最良の結果を出すように条件づけられます。

マニュアルによる DSP コーディングは非常にエラーが発生しやすく、動作しそうにみえるエラーがあってもパスします。デザインの複雑さのレベルは DSP を新しいデザインに使用するという決断を困難にします。エンジニアリングの労力はアナログデザインよりもはるかに高いです。しかし、DSP デザインを IsSpice4 によって解決するという方法(例えば、DSP Designer 内に含まれる特別なスケマティックモデルの利用、シミュレーション波形表示等)は、DSP のプログラミングをより簡単化、自動化でき、デザイン品質の向上を達成できます。

IsSpice4の実際のソリューションは LU 分解によって計算しています。しかし、平凡ではないマトリックス部分はマトリックスの右側 RHS はゼロで、結果、最終的な後退代入の定数係数になります。マトリックス・ソリューションは適切な連続の乗加算(MAC)命令によって得られます。マトリックス係数は一定の配列に格納されます。そして、状態変数は関連する係数に合った順にアクセスされます。MAC 命令はそれぞれの DSP によって異なるので、コードジェネレータ・アルゴリズムはターゲットの DSP に合わせます。

図 3, 連続導通モード(CCM)で動作するバックレギュレータ